Zadání

- Zapojte 7493 jako čtyřbitový čítač.

- Pomoci J-K klopných obvodů sestavte zapojení čtyřbitového čítače.

- Pomocí 7493 realizujte děličku pulsů 4 a 6.

- Záznam průběhů signálů proveďte s využitím přístroje – Logic Analyzer .

Teorie a postup

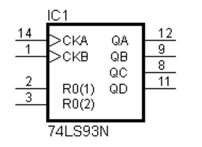

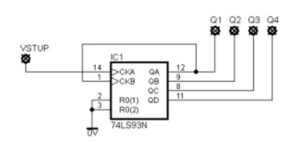

Binární čtyřbitový asynchronní čítač 7493 obsahuje celkem čtyři klopné obvody typu JK. První klopný obvod má spouštěcí vstup CKA a je schopný pracovat samostatně jako dělič dvěma. Následující 3 klopné obvody (spouštěcí vstup CKB) jsou zapojené jako čítač s modulem 8. Čítač má dva nulovací vstupy R0(1) a R0(2), kterými je možné všechny výstupy klopných obvodů vynulovat. Nulování se zajistí přivedením logických jedniček současně na oba vstupy R0(1) a R0(2). Toho lze využít pro zkrácení čítacího cyklu při návrhu čítače. Spojí-li se výstup QA se vstupem CKB lze obvod použít jako asynchronní čítač s modulem 16 v binárním kódu.

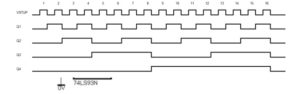

Změna logických úrovní na výstupech nastane během sestupné hrany vstupního signálu, který je přiváděn na VSTUP. Vstupní pulsy generujeme pomocí časové základny – TIME BASE. K indikaci výstupu časové základny použijeme statickou logickou sondu – LOG PROBE (bit A0). Stavy výstupních proměnných Q1 až Q4 zobrazíme pomocí statické logické sondy – LOG PROBE.

Obr.1 Schématická značka 7493

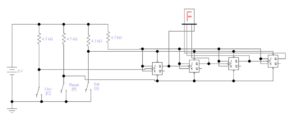

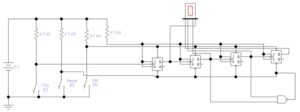

Obr. 2 Zapojení čtyřbitového asynchronního čítače s IO 74LS93

Obr. 3 Časové průběhy na vstupu a výstupech binárního asynchronního čtyřbitového čítače

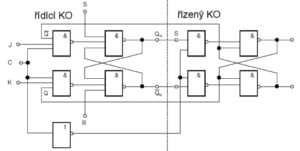

Obr. 4 Vnitřní struktura J-K klopného obvodu

Zapojení obsahuje dva řízené klopné obvody R-S, u nichž výstupy Q a /Q prvního jsou navázány na vstupy S a R (po řadě) druhého. Druhý klopný obvod se řídí invertovanými hodinovými impulsy a zpětná vazba je vedena z výstupu druhého klopného obvodu na vstup prvního. První klopný obvod se nazývá řídicí (master), druhý klopný obvod je řízený (slave). S náběžnou hranou hodinového impulsu se nastavuje úroveň na výstupech řídícího obvodu; řízený obvod je uzavřen, neboť úroveň na jeho hodinovém vstupu /C = 0. S úběžnou hranou hodinového impulsu se uzavírá vstup řídícího klopného obvodu a stav na jeho výstupu je kopírován řízeným klopným obvodem. Jeho výstupní úrovně jsou vedeny zpětnou vazbou na vstup řídícího obvodu, tam však nezpůsobí žádnou změnu, neboť tentokrát je řídící obvod uzavřen (C = 0). Asynchronní vstupy jsou zavedeny do řídicího klopného obvodu. Nastavíme-li asynchronními vstupy řídící klopný obvod, přesune se tato informace do řízeného klopného obvodu okamžitě (je-li C = 0), neboť mezi hodinovými impulsy je C = 0, tedy /C = 1; řízený klopný obvod, ovládaný signálem /C, je tedy otevřen.

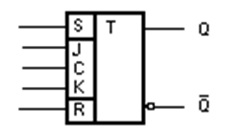

Obr. 5 Schématická značka J-K klopného obvodu

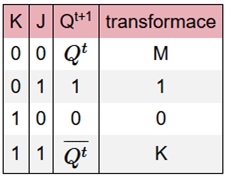

Obr. 6 Pravdivostní tabulka a stavový diagram J-K klopného obvodu

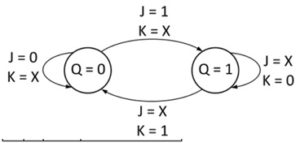

Obr. 7 Zapojení čítače pomocí J-K klopných obvodů

Obr. 8 Realizace děličky pulsů 6 pomocí J-K klopných obvodů

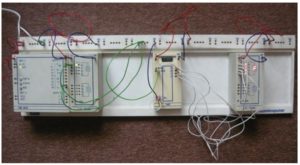

Obr. 9 Zapojení IO 7493 se stavebnici DOMINOPUTER

Otázky

- Lze využít integrovaný asynchronní čítač 74LS93 jako dělič?

- Kolik stavů má čtyřbitový asynchronní čítač?

- Nakreslete časové průběhy na vstupu a výstupech binárního asynchronního čtyřbitového čítače.

- Jakých klopných obvodů pro realizaci čítače využívá integrovaný čítač 74LS93?